Microelectronics

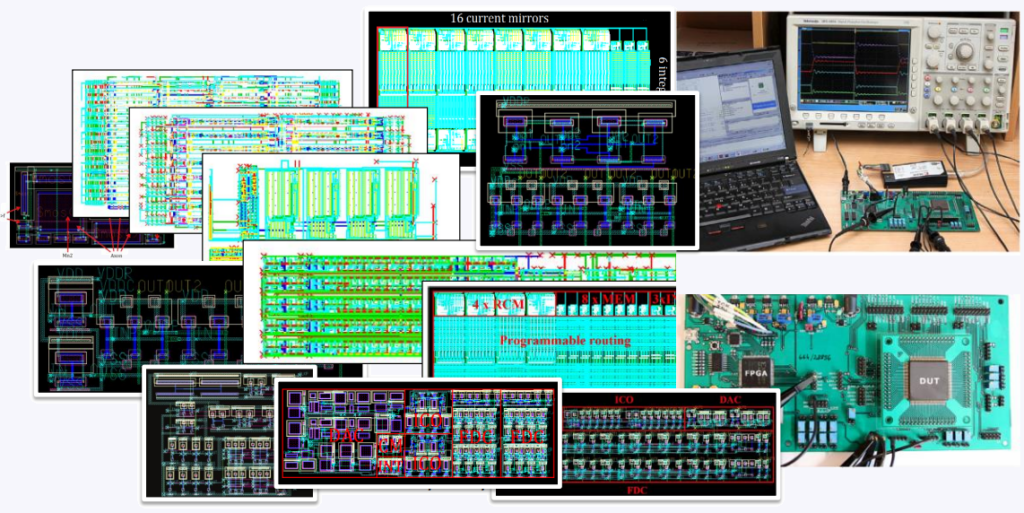

Our team has over twenty years of experience in designing VLSI circuits. We have access to nanometer technologies and commercial design tools. We represent the Poznań University of Technology in the Europractice consortium.

We operate in the field of both analog and digital electronics. In the design process, we use various methods to optimize and automate the generation of integrated circuit topography. VLSI solutions are often a complement to other projects we implement in the area of AI or hardware security.

The results of our research have been published in top international electronic journals and presented at prestigious international conferences. In the last few years, our team has defended three PhD theses and one habilitation in the field of VLSI.

We have implemented grants for research institutions and industry. Our largest VLSI project financed by Intel Labs, titled Pre-Silicon Design and Verification, concerns the implementation of Digital Logic Design and Embedded Systems Hardware Design technology.

Topics of our projects:

- Analog accelerators

- ADC/DAC

- FPAA

- Neural prostheses

- Neuromorphic circuits

- Filters and filter banks

- Preprocessors

- Biomedical signal processing

- Sensor data analysis

- Computation in tissues and cells

Grants

NCN Nr N N515 242937

Intel Labs 2023

Statutory Activities for Young Staff No. 09/94/DSMK/0058

Statutory Activities for Young Staff No. 09/94/DSMK/0052

Publications

Study of the Complexity of CMOS Neural Network Implementations Featuring Heart Rate Detection, P. Baryczkowski, S. Szczepaniak, N. Matykiewicz, K. Perz, S. Szczęsny // Electronics – 2023, vol. 12, iss. 20, s. 4291-1-4291-19

CMOS Perceptron for Vesicle Fusion Classification / M. Naumowicz, P. Pietrzak, S. Szczęsny, D. Huderek // Electronics – 2022, vol. 11, iss. 6, s. 843-1-843-15

0.50-V Ultra-Low-Power Σ Δ Modulator for Sub-nA Signal Sensing in Amperometry / Szymon Szczęsny, Marek Kropidłowski, Mariusz Naumowicz // IEEE Sensors Journal – 2020, vol. 20, no. 11, s. 5733-5740

60 pW 20 μm size CMOS implementation of an actual soma membrane / Szymon Szczęsny, Damian Huderek // Journal of Computational Electronics – 2020, vol. 19, iss. 1, s. 242-252

ADC based on a fully differential current mode integrator / Andrzej Handkiewicz, Marek Kropidłowski, Szymon Szczęsny, Mariusz Naumowicz // Analog Integrated Circuits and Signal Processing – 2019, vol. 100, no. 2, s. 327-334

Spiking Neural Network Based on Cusp Catastrophe Theory / Damian Huderek, Szymon Szczęsny, Raul Rato // Foundations of Computing and Decision Sciences – 2019, vol. 44, no. 3, s. 273-284

ADC z w pełni różnicowym integratorem w trybie prądowym / Andrzej Handkiewicz, Mariusz Naumowicz, Marek Kropidłowski, Szymon Szczęsny // Przegląd Elektrotechniczny – 2018, R. 94, nr 9, s. 22-25

HDL-Based Synthesis System with Debugger for Current-Mode FPAA / Szymon Szczęsny // IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems – 2018, vol. 37, no. 5, s. 915-926

Over rail-to-rail fully differential voltage-to-current converters for nm scale CMOS technology / Andrzej Handkiewicz, Szymon Szczęsny, Marek Kropidłowski // Analog Integrated Circuits and Signal Processing – 2018, vol. 94, iss. 1, s. 1-8

0.3 V 2.5 nW per Channel Current-Mode CMOS Perceptron for Biomedical Signal Processing in Amperometry / Szymon Szczęsny // IEEE Sensors Journal – 2017, vol. 17, no. 17, s. 5399-5409

Current-Mode FPAA with CMRR Elimination and Low Sensitivity to Mismatch / Szymon Szczęsny // Circuits, Systems, and Signal Processing – 2017, vol. 36, iss. 7, s. 2672-2696

High speed and low sensitive current-mode CMOS perceptron / Szymon Szczęsny // Microelectronic Engineering – 2016, vol. 165, s. 41-51

Current mode sigma-delta modulator designed with the help of transistor’s size optimization tool / Paweł Śniatała, Mariusz Naumowicz, Andrzej Handkiewicz, Szymon Szczęsny, J.L.A de Melo, N. Paulino, J. Goes // Bulletin of the Polish Academy of Sciences. Technical Sciences – 2015, vol. 63, no. 4, s. 919-922

SI-Studio, a layout generator of current mode circuits / Andrzej Handkiewicz, Szymon Szczęsny, Mariusz Naumowicz, Piotr Katarzyński, Michał Melosik, Paweł Śniatała, Marek Kropidłowski // Expert Systems with Applications – 2015, vol. 42, iss. 6, s. 3205-3218

Design automation of a lossless multiport network and its application to image filtering / Andrzej Handkiewicz, Piotr Katarzyński, Szymon Szczęsny, Mariusz Naumowicz, Michał Melosik, Paweł Śniatała, Marek Kropidłowski // Expert Systems with Applications – 2014, vol. 41, iss. 5, s. 2211-2221

Filter Design Based on Multi-port and Multi-dimensional gC Circuits, Andrzej Handkiewicz, Grzegorz Krzywoszyja, Wojciech Zajac, Mariusz Naumowicz, Circuits, Systems, and Signal Processing, pp. 1-26, 2025